游民星空 > > 正文

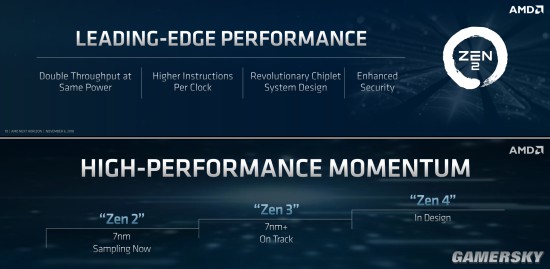

AMD 7nm Zen 2架构解析:吞吐量翻倍 前端重新优化

2018-11-07 12:35:55 来源:快科技 作者:上方文Q 编辑:听风飞舞 浏览:loading

而在浮点方面,Zen 2将浮点宽度翻了一番达到256-bit,载入存储带宽同样翻了一番,并提升了分发/回退带宽,所有模块都保持着很高的吞吐。

安全性方面,AMD重点强调了新架构可以在硬件层面免疫Spectre幽灵安全漏洞。

Zen 2架构支持更多核心,但并不是单纯地增加核心数量,而是采用了特殊的组合结构:EPYC霄龙最多单路64核心128线程,分为八个Die,每个Die内八个物理核心,同时外部还有一个单独的I/O Die,集成内存控制器、Infinity Fabric高速总线、I/O输入输出,专门负责联络各个Die与物理核心。

这种新的模块化设计更加灵活,可以单独针对每个模块进行优化、调配,同时借助I/O Die大大优化了整体延迟与功耗。

不过注意,CPU Die部分用的是7nm工艺, I/O Die部分则还是14nm,因为后者大部分都是模拟电路,对新工艺并不敏感,即便上了7nm也不会带来集成度、性能、功耗的明显改善,成本却会明显增加,所以采用了这种混合工艺模块组合。

事实上,Intel也正在同一颗芯片内尝试不同工艺的组合,都是出于同样的目的。

以上说的都是Zen 2架构的理论部分,最终落实到EPYC霄龙、Ryzen锐龙产品上,还会有不同的表现,但可以预料,新架构新工艺,必然会带来明显更高的频率、更低的功耗,而且无论桌面还是服务器,AMD这几年都会保持前后代兼容。

休闲娱乐

-

人妻感爆表的日本女主播 一直信奉肉腿神教的囧图

人妻感爆表的日本女主播 一直信奉肉腿神教的囧图

商k和普通夜店有什么区别?翻模可当碗的囧图

商k和普通夜店有什么区别?翻模可当碗的囧图

-

能让Ecup空杯的胸罩 大就是美白就是好的囧图

能让Ecup空杯的胸罩 大就是美白就是好的囧图

《地平线6》Steam简中首发多半差评!游戏进不去

《地平线6》Steam简中首发多半差评!游戏进不去

-

《地平线6》被怒喷政治正确!人物丑爆 不男不女

《地平线6》被怒喷政治正确!人物丑爆 不男不女

卡普空《识质存在》惨遭破解!存活不到一个月

卡普空《识质存在》惨遭破解!存活不到一个月

综合热点资讯

- 好莱坞女星穿着太大胆!外衣全透明 肉体清晰可见

- 冯提莫性感短裙造型开直播被封!网友热议原因

- 离谱!国产类魂新作《黑神话钟馗》登陆Steam

- 中南大学加油视频 181cm学长因帅出圈:已保研同济

- XBOX正式更名!网友直呼:经典回归 意义重大

- 44岁大叔坚持三年一拳超人训练法!最后效果惊了

- 性感大雷女模竟要缩胸!极品双峰即将退役

- 停更近一年:《明末》夏思源离职后首度“现身”!

- 意大利美女主持人露点走光 这傲人双峰太顶了啊!

- 黄仁勋疑似得灰指甲登热搜!网友:一个传染俩

单机游戏下载

- 《深海迷航2》官方抢先体验版下载

- 《魔法门:上古纪元》官方抢先体验版下载

- 《哥布林维克:窃贼大亨》官方正版下载

- 《Team Principal: A Racing Manager》官方正版下载

- 《BAZOOKA: Rhythm Game》官方正版下载

- 《八号窗口:千禧年》官方中文版下载

- 《Toad's Soul Hopper》官方中文版下载

- 《姆明:暖心冬日》官方中文版下载

好物推荐

-

发布时间:2026-05-15

-

发布时间:2026-05-15

-

发布时间:2026-05-15

游民星空联运游戏