AMD锐龙9000系列处理器首测:超越Intel登顶游戏最强王座

9000系锐龙处理器架构简介:

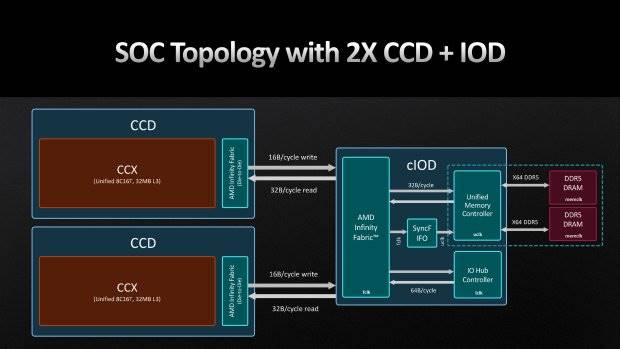

由于9000系锐龙处理器在内部整体架构方面并没有变化,仍然是采用了CCD+CCD+I/O Die的方式,所以完全可以拿之前7000系锐龙处理器的结构图来做参考。

同样的,由于单个CCD访问I/O Die写入的周期仅为读取一半的关系,可以理解为在内存写入方面,单CCD的9000系锐龙处理器仍有点小劣势。

当然,抛开架构不谈,9000系锐龙在内部改进还是蛮大的,通过基础TDP可以看出来,相较于7000系锐龙处理器的105W,9000系是在上边做了减法,使得TDP降至65W。TDP的降低意味着发热量降低,如何降低发热量的同时进一步提升性能(而不是像友商那样一味的堆性能不考虑散热),这就需要AMD的工程师们去精雕细琢了。

Zen5的提升主要有4点,分别是:

1,每个周期内可以执行更多的指令。

2,提升调度以及执行所需的带宽。

3,数据缓存带宽翻倍。

4,AI加速。

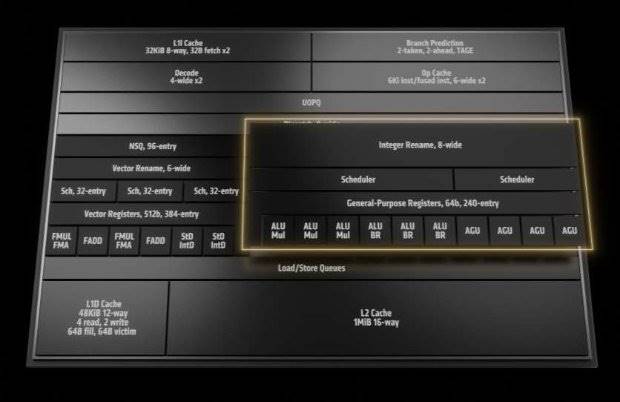

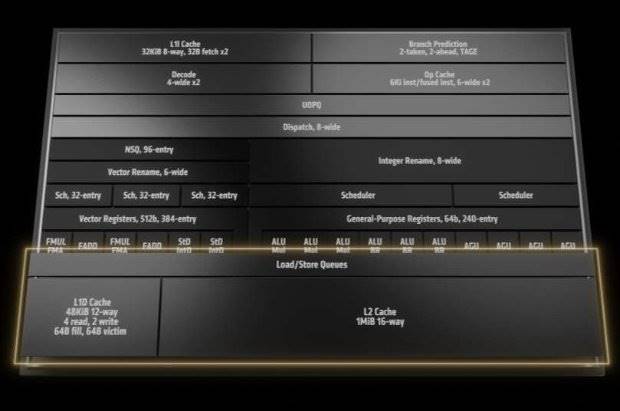

首先是前端方面的改进,周期获取与解码指令升级到了32B*2=64B,解码(Decode)由原来的单路变成了双路(4-wide X2共8条)。分发单元(Dispatch)由原来的6条增加到了8条,与分支预测相关的操作缓存(OP Cache)则是升级到了6*2共12条。

接下来是后端部分,整数单元(ALU)由3个升级成了6个,而地址生成单元(AGU)则是由3个升级成了4个。

由于解码(Decode)和分发单元(Dispatch)都是8条的关系,现在重命名寄存器(Integer Rename)也变成了8条,以保证处理效率的统一。

接下来是存取单元部分,在这里9000系锐龙处理器的每个1级数据高速缓存(L1D Cache)从之前的8路32KiB升级为12路48KiB。管线(LS Mem Pipes support Load/Store)升级为每周期4读取2写入。

从7000系列锐龙处理器开始就增加了对AVX 512指令集的支持,不过9000系列锐龙为其配备了完整的AVX 512指令集的配套设施,其中包括完整的512bit位宽以及6个具有双周期延迟的快速加法器(FADD)。

-

红色沙漠杀入畅销榜全球前五!玩家热议游戏质量

红色沙漠杀入畅销榜全球前五!玩家热议游戏质量

2B的丁字裤呢?《守望先锋》尼尔联动皮肤遭质疑和谐

2B的丁字裤呢?《守望先锋》尼尔联动皮肤遭质疑和谐

-

光与影对侵权案道歉!抱歉搞错了 我们没管好律师

光与影对侵权案道歉!抱歉搞错了 我们没管好律师

数毛社锐评新Xbox和PS6:Xbox的性能优势没有意义

数毛社锐评新Xbox和PS6:Xbox的性能优势没有意义

-

国产《湮灭之潮》新预告来了!画面无敌 美术绝佳

国产《湮灭之潮》新预告来了!画面无敌 美术绝佳

162cm学弟挑战160斤学姐 早期程序员鼓励师的囧图

162cm学弟挑战160斤学姐 早期程序员鼓励师的囧图

- 稳了!稳了!PS商店公开《GTA6》解锁时间

- 医生提醒不要模仿Ella“真空腹”:或诱发疝气

- 《生化危机9》丧尸集体“拉裤兜” 真相来了

- 绯红女巫被删限制级场景花絮流出!尺度太大不敢看

- 《lol》冠军中单Rookie官宣分手!甜蜜赛场伴侣终散场

- 《三角洲行动》毁号受害人发声!最新进展公开

- 大司马主播朋友称被给了500平米房子住!暂住搞直播

- 维密超模母女齐上阵!性感内衣大片火辣同框

- 道高一丈!D加密重大更新 多重防护堵死新型破解路径

- OnlyFans的含金量!艾丽范宁新剧正式预告:来钱真快

- 《1根香肠走江湖》官方中文版下载

- 《世界末日和她的房间》官方中文版下载

- 《Galactic Vault》官方中文版下载

- 《The Artifactory》官方中文版下载

- 《日本乡下生活》官方中文版下载

- 《Chilling Silence》官方正版下载

- 《The Lyra Signal》官方正版下载

- 《Haunted: Attack of the Dead Men》官方正版下载

-

发布时间:2026-03-11

-

发布时间:2026-03-11

-

发布时间:2026-03-11