Intel推3D立体封装结构CPU:10nm工艺 仅指甲盖大小

半个世纪以来,半导体行业一直在魔鬼般的摩尔定律的指导下飞速前进,工艺、架构、技术不断翻新,但任何事情都有个变化的过程。近年来,整个半导体行业明显感觉吃力了很多,很多老路已经行不通或者跑不快了,要想继续前行,必须拓展新思路、新方向。

比如说处理器芯片封装,以往大家都是习惯于在一个平面上摊大饼。随着集成模块的多样化、工艺技术的复杂化,这种传统方式越来越难以为继,跳出来走向3D立体的世界也就成了必然。

其实对于3D堆叠式芯片设计,大家应该并不陌生,很多芯片领域都已经做过尝试,有的还发展得极为成熟。最典型的就是NAND闪存,3D堆叠式封装已经做到了惊人的96层,未来还会继续加高,无论容量还是成本都可以更加随心所欲,不受限制。

不过在最核心的CPU处理器方面,受制于各种因素,封装方式一直都没有太大突破,变来变去也都是在一块平面基板上做文章,或者是单芯片,或者是多芯片整合。

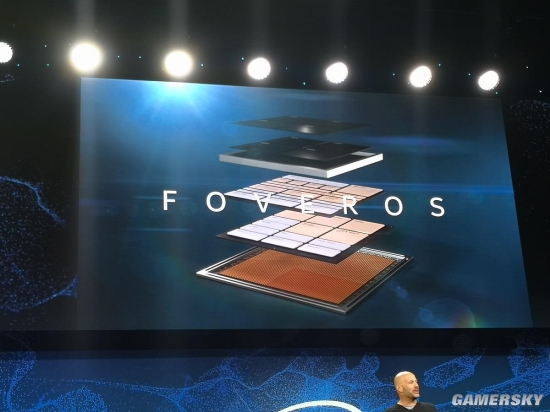

最近,Intel提出了革命性的Foveros 3D立体芯片封装技术,首次为CPU处理器引入了3D堆叠式设计,堪称产品创新的催化剂,或将成为CPU处理器历史上一个重要的转折点。

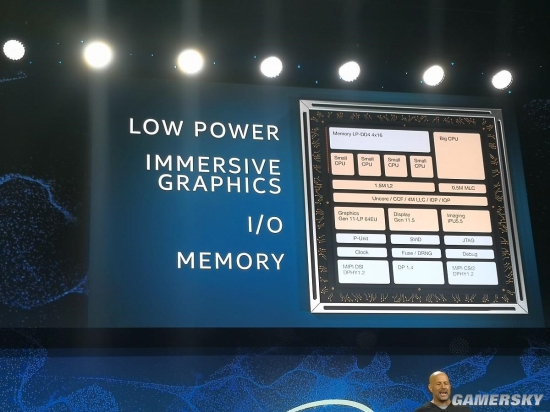

Intel Foveros 3D封装技术带来了3D堆叠的显著优势,可实现逻辑对逻辑(logic-on-logic)的集成,为芯片设计提供极大的灵活性。

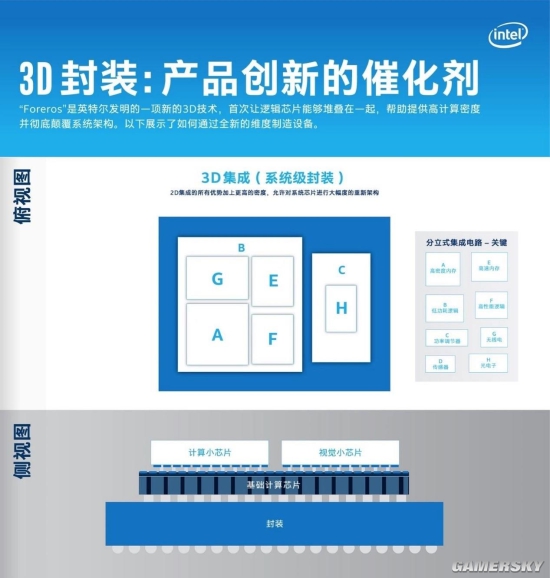

它允许在新的设备外形中“混搭”(mix and match)不同工艺、架构、用途的技术IP模块、各种内存和I/O元件,使得产品能够分解成更小的组合,同时将之前分散、独立的不同模块结合为一体,以满足不同应用、功耗范围、外形尺寸的设计需求,以更低的成本实现更高的或者更适宜的性能。

其实在此之前,Intel曾经应用过一种2D集成技术“EMIB”(嵌入式多芯片互连桥接),把不同工艺、功能的IP模块整合到单一封装中,相比传统2D单片设计更有利于提高良品率、提升整体性能、降低成本、加快产品上市速度,典型产品代表就是集成了Intel八代酷睿CPU、AMD Vega GPU图形核心的Kaby Lake-G系列。

Foveros则进化到了3D集成,延续2D集成各种优势的同时,加上全新水平的集成密度和灵活性,首次让逻辑芯片可以堆叠在一起,彻底颠覆并重新构建了系统芯片架构。

在Intel提供的Foveros 3D堆叠封装示意图上,可以清楚地看到这种盖楼式设计的巧妙之处:

最底部的封装基板之上,是核心的基础计算芯片,再往上可以堆叠计算、视觉等各种模块,高性能逻辑、低功耗逻辑、高密度内存、高速内存、传感器、功率调节器、无线电、光电子等等就看你需要什么了,无论是Intel IP还是第三方IP都可以和谐共处,客户完全可以根据需要自由定制。

当然,如何处理不同模块之间的高速互连,确保整体性能、功耗等都处于最佳水平,无疑是非常考验设计能力和技术实力的,TSV硅穿孔、分立式集成电路就是其中的关键所在。

Intel还强调,3D封装不一定会降低成本,但重点也不在于成本,而是如何把最合适的IP放在最合适的位置上,进行混搭,这才是真正的驱动力。

-

女巨人最巨大的是哪里?请你不要到处扣扣的囧图

女巨人最巨大的是哪里?请你不要到处扣扣的囧图

对巨乳不感兴趣的是没碰到自己的 满足于烧鸡的囧图

对巨乳不感兴趣的是没碰到自己的 满足于烧鸡的囧图

-

什么样的腿才是完美腿型?大幂幂是真的大的囧图

什么样的腿才是完美腿型?大幂幂是真的大的囧图

劳拉新形象太丑胸围被大砍!祖国人看了都没食欲

劳拉新形象太丑胸围被大砍!祖国人看了都没食欲

-

国产大作湮灭之潮登央视!中国游戏也能讲国际故事

国产大作湮灭之潮登央视!中国游戏也能讲国际故事

全新国产虚幻5《鲲歌》首曝!能打篮球 3D动作肉鸽

全新国产虚幻5《鲲歌》首曝!能打篮球 3D动作肉鸽

- “乳神”没了!40岁达达里奥新照曝光 胸部缩水严重

- 杨奇发黑神话新视频!工作到凌晨2点左右才下班

- 全网泪目!一位父亲在《识质存在》中找到已故女儿

- 霍格沃茨之遗又免费送了!5月3日截止 快快上车

- 《GTA6》新预告消息曝光!真的不会再跳票了

- 日本酒吧推“正妹吐奶咖啡”网友痛批:低俗恶心!

- 46岁陈冠希近照曝光!胡子稀疏老态明显

- 艾丽范宁裸体新剧剧照尺度拉满!勾舌媚眼欲望十足

- 好莱坞女神前男友爆隐私:"胸很大"还"天天拽我上床"

- 李小冉露出白花花全脂胳膊 因“毫无运动痕迹”热搜

- 《Team Principal: A Racing Manager》官方正版下载

- 《BAZOOKA: Rhythm Game》官方正版下载

- 《八号窗口:千禧年》官方中文版下载

- 《Toad's Soul Hopper》官方中文版下载

- 《姆明:暖心冬日》官方中文版下载

- 《这是我的宝藏!》官方中文版下载

- 《全球救援》官方中文版下载

- 《Snap & Grab》官方正版下载

-

发布时间:2026-05-02

-

发布时间:2026-05-01

-

发布时间:2026-05-01