AMD锐龙5900X首测:捅破英特尔游戏性能天花板

ZEN3架构的重大改进之处有哪些?

由于时间有限,有关ZEN3架构以及Ryzen 5000系列一些晦涩难懂的技术话题留待以后探讨,这里先说几点最核心的变化,它们大体上都是最先前最欠缺的。

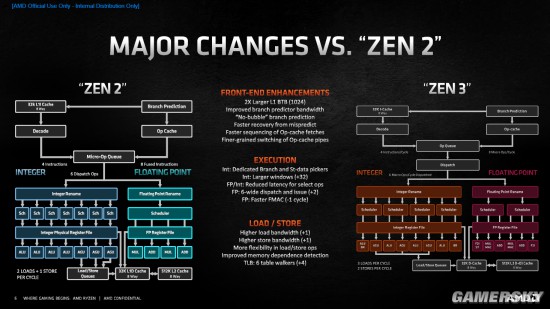

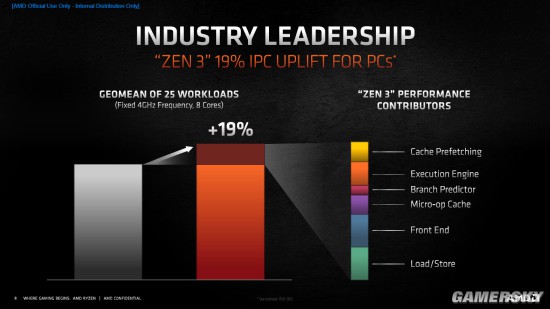

首先,在每个核心内部,ZEN3架构重新设计和部署了流水线,将L1缓冲区加倍,提高指令预测的速度,尤其是调整了整数计算和浮点计算的结构布局,得到更灵活、更流畅的指令调度,选择指派浮点和整数计算的延迟更低,使得需要处理大量数据的长指令的执行效率得到显著提升,而这方面也是之前AMD相比Intel最大的劣势。

因为再多核心线程,再多的并行计算也无法将单一指令的完成时间提前,而这正是需要即时运算的游戏所仰仗的性能,或称之为"延迟"更恰当,它代表从指令发出到CPU完成任务的时间,同时这也印证了为何核心线程的数量发展突飞猛进,但单核频率对游戏性能的影响始终很大。

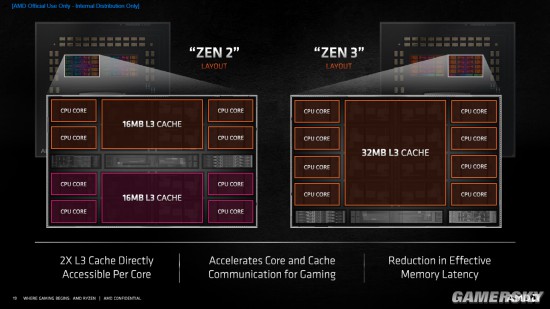

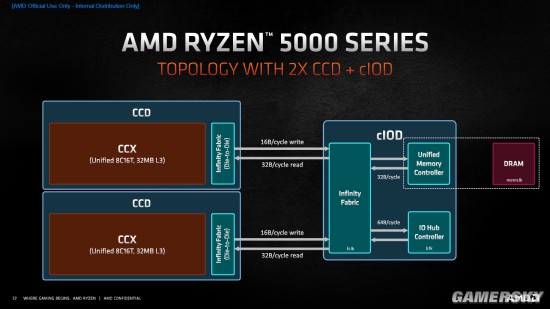

ZEN3在SOC结构上做了重大调整。原来的ZEN2每个内核含有两个CCX,每个CCX包含4个核心和并每核连到共享16MB的L3缓存。这样当一个CCX中的核心需要访问另一个CCX的L3缓存时,它就得通过CCX之间的联络,尽管每个内部的效率极佳,但是跨CCX访问时延迟又会变的较高。

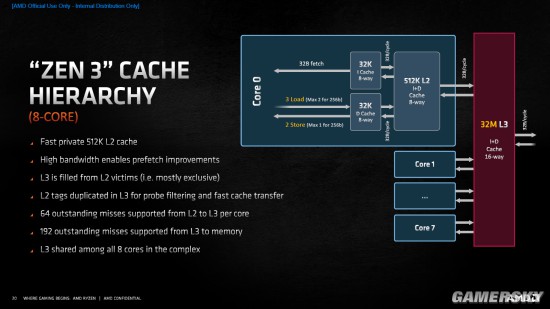

ZEN3相当于是将原来的两个CCX合二为一,每个CCD只有一个CCX,包含8个核心和共享的32MB缓存,核心与缓存之间采用类似Ringbus的方式链接。Ringbus即环形总线是一种简单有效的经电设计,可利用最少的晶体管和核心面积使更多的核心访问一整个共享L3缓存,但是有利有弊,过大的环形总线又会加大核心之间互访的延迟。明智的做法就是将环上的核心数量控制在一定限度内。ZEN3的将每个CCD的Ringbus控制在8个核心的规模,相当于一颗i7 10700K。

ZEN3的IOD依然使用12nm工艺,它与CCD之间通讯的Infinity Fabric读写速率相比ZEN2没有变化,依然是每个时钟周期16/32的配置。但是随着工艺制程的进步,这一代IOD中内存控制器即Uncore得以提升,因而可以与内存和FCLK同步运行在更高的物理频率,可更充分发挥高频率DDR4内存的性能。此前在第一代ZEN架构时AMD曾饱受此困扰,内存频率一度难以稳定在DDR4-3000以上。

百尺竿头更进一步,CPU要在频率以外的领域提高一点效能都是十分艰难的。将以上点滴进步汇聚到一起,AMD官方宣称Ryzen 5000处理器的IPC(时钟周期指令速率)提高了19%。

实际情况是否真如AMD所述,下面的测试将揭晓答案。

- 第1页:ZEN3来袭,CPU迎来天王山之战

- 第2页:ZEN3架构的重大改进之处有哪些?

- 第3页:测试平台搭建与分析

- 第4页:Ryzen 9 5900X工况展示

- 第5页:基准测试:浮点与整数计算性能

- 第6页:基准测试:图像渲染性能

- 第7页:基准测试:3DMARK与PCMARK

- 第8页:基准测试:内存与存储性能

- 第9页:《刺客信条:奥德赛》游戏实测

- 第10页:《无主之地3》游戏实测

- 第11页:《死亡搁浅》游戏实测

- 第12页:《孤岛惊魂5》游戏实测

- 第13页:《地平线:零之曙光》游戏实测

- 第14页:《战争机器5》游戏实测

- 第15页:《地铁:离去》游戏实测

- 第16页:《古墓丽影:暗影》游戏实测

- 第17页:《三国:全面战争》游戏实测

- 第18页:《CS:GO》游戏实测

- 第19页:《英雄联盟》游戏实测

- 第20页:总结:真正意义上的并驾齐驱

-

搬屎群友是大胸美少女 技校配不上大学的囧图

搬屎群友是大胸美少女 技校配不上大学的囧图

少女拍片胸部走光 别人的老婆就是劲的囧图

少女拍片胸部走光 别人的老婆就是劲的囧图

-

Steam天价游戏标价3600元!国区竟真有玩家买了

Steam天价游戏标价3600元!国区竟真有玩家买了

PS6全方位泄露汇总!售价 发售时间与独占游戏等曝光

PS6全方位泄露汇总!售价 发售时间与独占游戏等曝光

-

惊呆!手机能跑《大表哥2》:流畅游玩无压力

惊呆!手机能跑《大表哥2》:流畅游玩无压力

Switch 2新手柄超吸睛!自定义RGB灯效 视觉效果炸裂

Switch 2新手柄超吸睛!自定义RGB灯效 视觉效果炸裂

- PS6全方位泄露汇总!售价 发售时间与独占游戏等曝光

- “汉尼拔”高中毕业照让网友炸锅!这真是吃人恶魔?

- 假名媛别乱脱丝袜!一咖啡店700字进店须知走红

- 电竞冠军因庆祝动作被判负!玩家抗议:裁判才该开除

- NASA误播宇航员半裸画面 女网友大赞身材太棒

- 《生化危机10》突遭泄露!全新女主角惊艳曝光

- 知名女演员被查出桥本病:不得不彻底告别外卖

- 田曦薇深V旗袍直播因太有料被封!雪白半胸险走光

- 因毁容惨遭霸凌!巴西网红接受隆胸手术重塑自信

- 《生化危机9》格蕾丝COS!不穿裤子大秀美臀

- 《Card Coder》官方中文版下载

- 《Fortune Seller》官方中文版下载

- 《暗夜运输者》官方中文版下载

- 《World Pole Stone Dusk》官方正版下载

- 《Rabbit Samurai》官方中文版下载

- 《埃尔希乔》官方中文版下载

- 《宁静之海》官方中文版下载

- 《枪X狗X复仇》官方中文版下载

-

发布时间:2026-04-08

-

发布时间:2026-04-07

-

发布时间:2026-04-07